RFID干货专栏|33 Indy阅读器芯片详解

RFID干货专栏概述

经过20多年的努力发展,超高频RFID技术已经成为物联网的核心技术之一,每年的出货量达到了200亿的级别。在这个过程中,中国逐步成为超高频RFID标签产品的主要生产国,在国家对物联网发展的大力支持下,行业应用和整个生态的发展十分迅猛。然而,至今国内还没有一本全面介绍超高频RFID技术的书籍。

为了填补这方面的空缺,甘泉老师花费数年之功,撰写的新书《物联网UHF RFID技术、产品及应用》正式出版发布,本书对UHF RFID最新的技术、产品与市场应用进行了系统性的阐述,干货满满!RFID世界网得到了甘泉老师独家授权,在RFID世界网公众号特设专栏,陆续发布本书内容。

扫码观看本章节视频讲解

5.2.4 ImpinjIndy阅读器芯片详解

Impinj的Indy系列阅读器芯片在全球市场占有统治地位。在采用专用集成芯片方案的全球中端阅读器市场中,几乎100%采用Indy系列芯片。ImpinjIndy阅读器芯片的前身是Intel公司开发的阅读器芯片Intel R1000,后Intel将该业务板块卖给了Impinj,改名为IndyR1000。R1000芯片是最早的超高频RFID阅读器集成芯片。Impinj后续在R1000的技术上又开发了带有载波消除功能的高性能阅读器芯片R2000,从此确定了Indy系列在阅读器芯片市场的领导地位。

01、Indy阅读器芯片系列

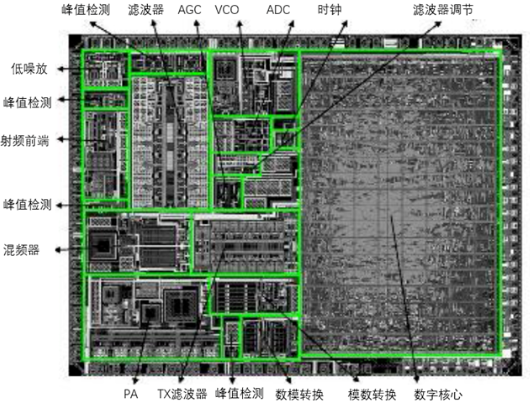

至今ImpinjIndy共发布3款阅读器芯片分别是R1000、R2000和R500,其中R1000的发布时间为2008年,R2000和R500发布时间为2010年。这三款阅读器芯片均采用0.18um SiGe BiCOMS工艺,如图5-31所示为R2000的硅芯片图。

图5-31R2000的硅芯片图

其中SiGe为硅锗材料,其特点为:高频特性良好,材料安全性佳,导热性好,而且制程成熟、整合度高,成本较低。

其中BiCOMS工艺的特点为:CMOS工艺和BiPolar工艺是两种主要的硅集成电路工艺,它们有各自的优点。CMOS器件有集成度高、功耗低、输入阻抗高等优点。BiPolar器件有截止频率高、驱动能力大、速度快、噪声低等优点。它们的优缺点正好互相补充,将它们集成到同一芯片上形成BiCMOS工艺,制得的器件性能定将超出单一工艺。由于Indy阅读器芯片中具有数字协议及处理部分,又需要射频高性能,因此采用SiGe材料和BiCOMS工艺的组合最合适,而0.18um工艺具有很好的性价比,因此Impinj采用此选择。

作为全球最早出现的阅读器芯片,Indy系列芯片具有如下优点:

集成度高

集成了大约90%的射频器件;

极大降低了成本;

可以作为RFIDModem;

适合于嵌入式应用。

灵活性强

支持多种的阅读器设计模型;

尺寸小(R500和R2000芯片9mmx 9mm;R1000芯片8mm x 8mm);

相对于分立设计功耗较小。

支持行业主要标准

ISO 18000-6B,ISO18000-6C,ISO 18000-6D(IPICO);

EPCglobal Class 1 Gen-2。

支持全球频段

840MHz – 960MHz;

符合SRRC、FCC,ETSI规范要求。

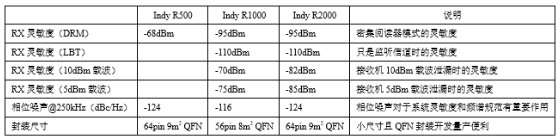

如表5-1所示为Indy系列三款芯片的差异参数表:

表5-1Indy系列芯片对比

通过表5-1可以看出,在不同的情况下,阅读器的灵敏度是不同的,其中R2000芯片具有最好的载波消除特性,可以在10dBm载波泄漏的环境下依然保持很高的灵敏度。而R1000的芯片随着载波泄漏信号的增加灵敏度下降的厉害。R500芯片定义为中低端芯片,因此其灵敏度被锁死在-68dBm,但这并非坏事,对于近距离的读写器,其稳定性优于R1000和R2000。R500和R2000芯片是在R1000芯片基础上开发出来的,因此锁相环的相位噪声有所提高,由于增加了载波抵消等功能,其管脚数量有所增加,因此采用略大的封装。

02、Indy芯片架构

(1)R1000

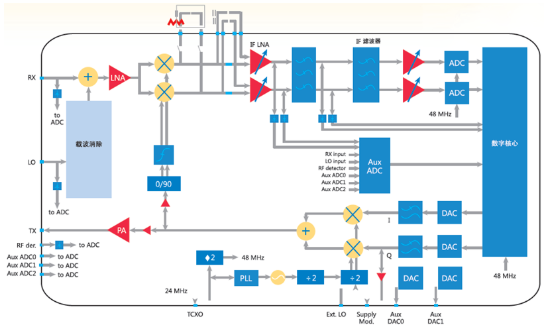

如图5-32所示为R1000芯片的框图,该芯片包含射频前端模块和数字模块,其中接收机采用零中频的一次变频方案。与传统的零中频接收机不同点在于锁相环PLL通过发射电路给接收电路的混频器提供本振信号,而非锁相环分别给发射机和接收机提供本振信号,这是由于超高频RFID阅读器RX信号的载波是由自身发出的。

图5-32Indy R1000芯片框图

标签反向散射的信号通过天线到达R1000接收机入口RX,然后通过低噪声放大器(LNA),将微弱的信号放大,再通过功分器,分为I/Q两路信号,并与本振信号相乘完成下变频。此时的信号具有很强的直流偏移,因此需要通过一个大电容的AC耦合,滤掉直流偏移影响。此时的标签有效信号已经变成了中频信号,再通过中频低噪放(IF LNA)和中频滤波器(IFFilter)。此时的信号具有较好的信噪比和解调性能,再通过一个可变增益放大器,其目的是调制信号幅度保证ADC采样精度。最终模拟基带处理好的信号通过sigma delta ADC变为数字信号进行数据处理。

当阅读器需要发送命令时,波形发生器会产生需要的波形数字文件,再通过sigma delta DAC转化为模拟信号,经过滤波后与本振相乘,完成上变频,成为超高频段的调制信号,再经过功率放大器输出芯片。

芯片的数字模块具有许多功能,包括数字信号处理,数字调制解调功能,以及数字接口管理和芯片电源管理等。

(2)R2000

如图5-33为IndyR2000的芯片框图,其设计框架与R1000芯片基本相同。对比R1000芯片,其增加了载波抵消模块,大大提高了载波泄漏时的灵敏度。同时,还改善了DRM滤波器,支持2阶和高阶片外滤波器,从而实现更好的滤波效果。另外很重要的一点是R2000芯片大幅提升了锁相环PLL的相位噪声,不仅对灵敏度有改善,还对符合全球无线电规范的产品开发有帮助。

图5-33Indy R2000芯片框图

R500芯片其实就是R2000芯片的简化版,其基本参数完全相同,晶圆也是同一颗,只是在封装测试时在固件中锁死载波抵消功能,并在芯片封装时去掉与载波消除相关的Pin脚的连接。

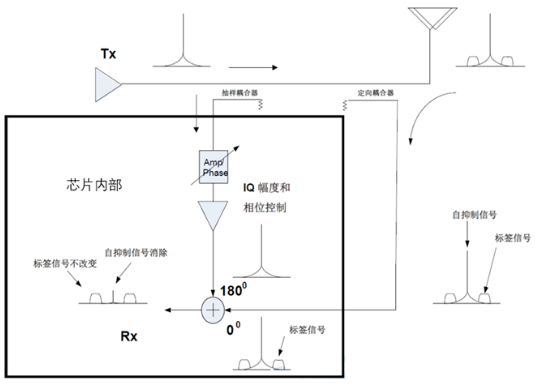

03、IndyR2000载波抵消

在5.2.2节中,已经介绍了载波泄露消除技术的实现方式,此处针对R2000芯片的载波抵消电路展开剖析。如图5-34所示,为R2000芯片内部载波抵消电路示意图。载波抵消电路是在芯片内的一个信号相加的电路,通过产生反向的载波,与接收端的泄漏载波相互抵消,从而抑制载波泄漏的大小。该电路实现方式为:

通过抽样耦合器从芯片的发射端引出一路参考信号。

将参考信号通过一个无源、低噪声的90°多相位滤波器,输出为四路信号:+I、-I、+Q、-Q。

通过调整这四路的I/Q信号的大小,可以实现一个与接收机泄漏载波大小相同、相位相差180°的信号。通过两个信号相加后(载波抵消后)的信号强度判断是否达到载波消除的预期。

理论上,这个抵消信号具有与接收到的泄漏载波相同的相位噪声,当两个信号抵消时,系统的噪声(发射机自带再生)也会相互抵消,因而有效信号的信噪比也会有所提升。

图5-34R2000芯片内部载波抵消电路

该电路存在一些缺陷:

由于抵消信号是从发射电路中耦合出来的,其信号强度不会特别大,因此对于很大的载波泄漏信号无法进行有效的载波消除。

调整四路I/Q信号大小产生抵消信号的过程需要经过多次尝试,尝试的次数越多抵消效果越好,但是消耗的时间越长,需要在载波消除效果和扫描时间中寻找折衷点。

四路I/Q信号的精度是有限的,精度越高可以产生相位与幅度更匹配的抵消信号,但其精度与成本及扫描时间相关,因此也需要寻找折衷点。

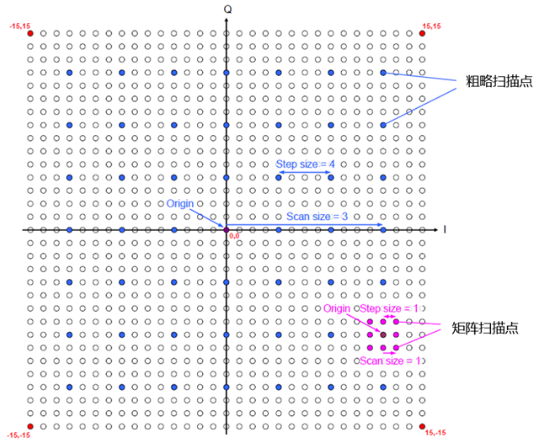

在上述讨论中,I/Q信号的精度、载波抵消的响应时间等问题都需要折衷考虑,经过对市场需求的理解,Impinj给出了一套快速寻找抵消信号的算法。R2000芯片将输出四路信号:+I、-I、+Q、-Q做4比特量化,每个信号的大小为0到15,因此整个复频域空间共有31×31=961个点。只要在这961个点中尝试,可以找到相对最合适的抵消信号,此参数的选择是经过折衷考虑的结果。

为了提高寻找效率,R2000给出了一套快速寻找匹配点的算法,如图5-35所示,首先在复平面内粗略扫描一遍,寄存器会记录下每个扫描点对应的加法器后的功率计度数。粗略扫描结束后从寄存器中找到度数最小的点,并记录下来。下一轮扫描为详细扫描,将围绕刚刚记录下的点周围3×3的格子进行扫描(矩阵扫描),同时记录在寄存器中,寻找新的度数最小点。如果新的度数最小点不是上一个度数最小点,则进行下一轮详细扫描,继续对周围3×3的格子中未扫描的点进行扫描,直到无法找到新的最小点,结束扫描。通过上述算法不必对整个星座图遍历一遍,可以大大提升效率。当然读者们也可以通过自己的算法减小扫描时间。

图5-35复频域快速匹配点的算法

当R2000采用3M/s的数据采样频率实现SJC校准,且针对每个点的采样次数为16和8个样本,采样时间为5.3us和2.6us。执行一次粗略全扫描共需要49次,因此需要392us。一个3×3矩阵扫描时间为72us。为了获得更好的载波抵消效果,最好重复多次寻找合适的匹配点。在实际应用中,每次阅读器发出命令之前,都会先启动SJC电路完成载波消除。

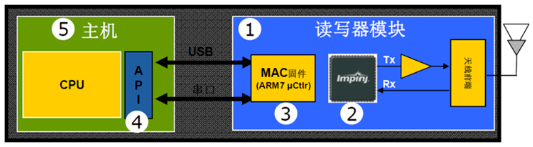

04、Indy芯片使用架构和开发

如图5-36所示为Indy芯片的使用架构图,图中阅读器模块由Indy阅读器芯片、ARM7处理器(MCU)、功率放大器和隔离器件组成。其中ARM7处理器中下载了Indy芯片的固件,包括Gen2协议,射频控制和接口等,通过调用Indy芯片的寄存器控制上述功能。主机通USB或串口与MCU相连,通过API控制阅读器模块工作。

图5-36Indy芯片的使用架构图

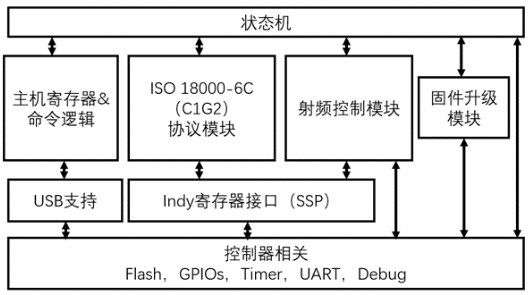

如图5-37所示为Indy芯片的固件架构图,该程序代码在ARM7芯片中,其中包括:

控制相关内容(Flash、GPIOs、定时器、串口、Debug);

状态机管理;

Indy寄存器接口(SSP)其中包换Gen2协议和射频控制模块;

固件升级模块;

主机寄存器和命令逻辑。

图5-37Indy芯片的固件架构图

ARM7固件内部Flash分三块,分别是:

Bootloader,提供系统的恢复和升级机制。

MAC固件,管理Modem控制器和主机接口寄存器。

OEM配置,静态设置寄存器,包括区域设置、主机接口设置、校准数据和板级诊断选项。

登录

登录

注册

注册