一文看懂 | 芯片是怎么来的?

什么是芯片?

芯片是半导体元件产品的统称,是电子学中将电路小型化的一种方式。虽然,在日常生活中,我们常将芯片、集成电路和半导体混同使用,但它与半导体和集成电路其实略有不同,通常半导体指的是一类材料的总称,集成电路是用半导体材料加工而成的小型化电路的大型集合,而芯片则是由一种或多种类型的集成电路形成的产品。如果将其映射到生活中,那么半导体是纤维,集成电路布料,而芯片则是衣服,这样是不是很好理解了呢?

时间轴上的 “芯”路历程

图源:Computer History Museum

从上述定义可知,讲芯片的发展史,核心就是要讲清楚半导体材料和集成电路的发展史。

集成电路的早期概念可以追溯到 1949 年,当时来自西门子的一位德国工程师 Werner Jacobi 在助听器中采用了一个专利,在该专利中就提到了在三级放大器中实现了五个晶体管排布在同一基板上的技术,并实现了助听器的小型、低价化。

1952 年,一位名叫 Geoffrey Dummer 的英国国防部皇家雷达局科学家在华盛顿质量电子元件进展研讨会上向公众提出了集成电路的概念。电工实验室的 Sidney Darlington 和 Yasuro Tarui 又进一步提出了类似的芯片设计,只是此时的集成电路还是非电气隔离的。

1957 年,贝尔实验室的 Mohamed M. Atalla 开发出了通过热氧化使硅表面实现电稳定的表面钝化工艺,该表面钝化工艺隔离了单个的二极管和晶体管,从而使硅基单片集成电路芯片成为可能。

1958 年,来自德州仪器的 Kilby 成功演示了集成电路的第一个工作示例,并于次年申请了发明专利,该专利后来荣获了 2000 年诺贝尔物理学奖,但是该集成电路的工作需要外部连线的配合才能实现工作,也就只能算是混合集成电路,谈不上真正意义上的单片集成电路芯片。

1959 年,仙童半导体的 Jean Hoerni 在表面钝化工艺的基础上实现了平面工艺,来自 Sprague Electric 的 Kurt Lehovec 将隔离技术扩展到单个硅片上的独立晶体管。说白了就是,每个晶体管尽管是嵌入到了同一块硅上,却都能独立运行。在此基础上,同样来自 Sprague Electric 的 Robert Noyce 同年发明了世界上第一款单片集成电路芯片。

1960 年,贝尔实验室的 Mohamed M. Atalla 又提出了 MOS 集成电路芯片,对比双极性晶体管,MOSFET 更易形成电气隔离。

MOS 集成电路的出现奠定了当代集成电路芯片的基础,随着技术的不断精进,到 1964 年,MOS 芯片已实现了比双极芯片更高的晶体管密度和更低的制造成本。

MOS 芯片的复杂度进一步以摩尔定律所预测的速度在增加,从 1960 年代后期的大规模集成(LSI),经历 1970 年代的超大规模集成(VLSI),到 1980 年代的超大规模集成(VLSI)和甚大规模集成(ULSI),再到现在最顶尖的 7nm 技术和系统级芯片。在这过程中,我们经历了一次前所未有的科技革命,芯片或者说集成电路彻底改变了人们的工作、生活方式。

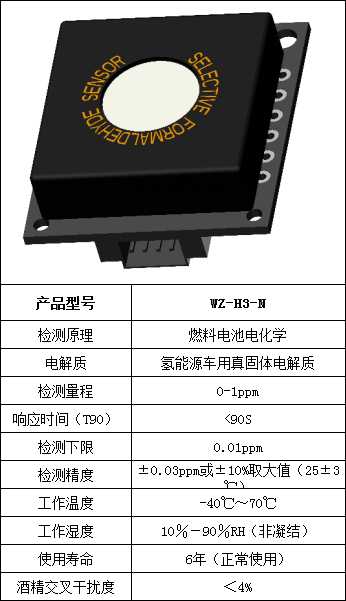

一群硅基芯片的诞生过程:设计+制造+测试

来源:知网论文

设计篇

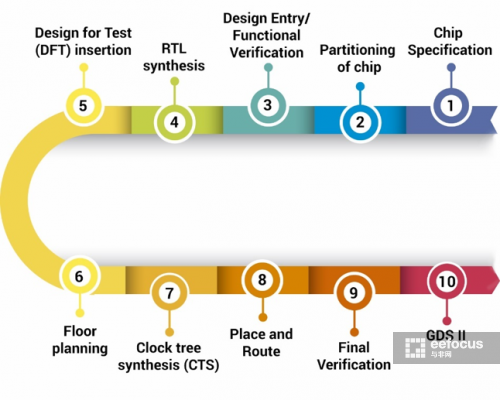

图源:einfochips

规格制定

在芯片设计公司内部,设计一枚芯片的第一步是通过管理和数据分析起草一份提案,使该该设计能从一开始就满足行业细分要求。此时高层设计人员会开会,进行可行性分析,并在此基础上确定芯片的功能和运行方式,并确定性能、功能、物理尺寸、制造技术和设计技术等主要设计参数。

架构定义

定义系统的基本规范,比如浮点单元等;确定要使用的系统,比如精简指令集计算机(RISC)或复杂指令集计算机(CISC);敲定 ALU 缓存大小的数量等。

功能设计

定义系统的主要功能单元,从而有助于识别单元之间的互连要求,还有每个单元的物理、电气规格。

逻辑设计

开发出布尔表达式、控制流、字宽、寄存器分配等,并采用 VHDL 或 Verilog HDL 硬件描述语言将功能用代码描述出来,形成寄存器传输级别(RTL)代码。

电路设计

逻辑设计给出了简化的逻辑实现,而电路设计则是以网表的形式进一步将该逻辑表示出来,网表通常由门、晶体管和各种互连组成,而电路设计的效果可以由仿真得到。

物理设计

在此步骤中实现了网表到其几何表示的转换,其结果称为布局,它可以从功能上对综合后的网表进行验证。此步骤遵循一些预定义的固定规则,例如 lambda 规则,该规则提供了组件大小、比例和间距等确切的详细信息。下一步是对完成布线的物理版图进行功能和时序上的验证,验证项目通常包括 LVS、DRC、ERC 等,当然还包括一些功耗分析以及可制造性分析。

设计工艺导出

这是芯片设计的最后一步,即将设计工艺文件按照芯片代工厂的要求导出来,设计公司保留原设计稿可做灵活性的修改,而相对定版的工艺文件——物理版图以 GDS II 的文件格式交由芯片代工厂作为制造依据。

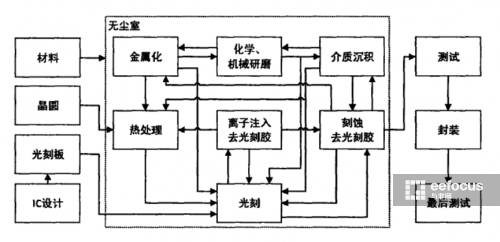

制造与测试篇

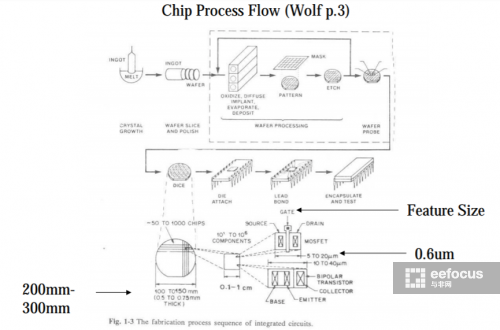

图源:Joseph A. Elias, PhD

打开工艺的卷轴,里面记录了沙子的升华史,我们通过它,了解到了芯片是如何制成的。

提炼单晶硅锭

图源:VIDHYARTHE

最廉价的硅来源非沙子莫属,因此半导体材料中采用的硅元素就是从沙子(SiO?)中提取出来的。通常,生产单晶硅锭的公司会将沙子从的硅元素提取出后来经过高温整形、多次提纯等手段得到电子级硅(EGS),纯度为 99.9999%。然后将纯硅在 1400oC 的锅中融化,把包含所需晶体取向的小晶种插入熔融的硅中,再缓慢地(1 毫米 / 分钟)拔出,这样硅晶体就被制造成了圆柱形的单晶硅锭,单个单晶硅锭的重量约为 100 公斤。

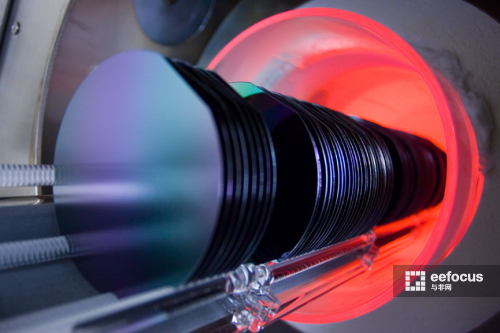

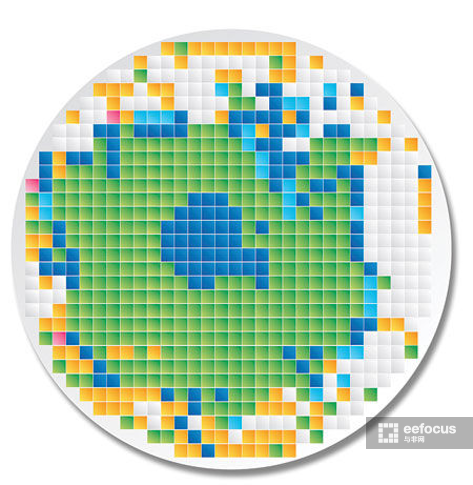

晶圆加工

图源:Cismst

晶圆加工主要包含两个步骤,第一步是将单晶硅锭横向锯成圆盘,再进行抛光和晶体定向,得到如镜面般平整的晶圆。第二步是对晶圆进行热氧化,这个时候纯硅会经过充氧的高温炉,从而在表面形成一层很薄的二氧化硅,作为晶体管的进时栅极氧化物层。

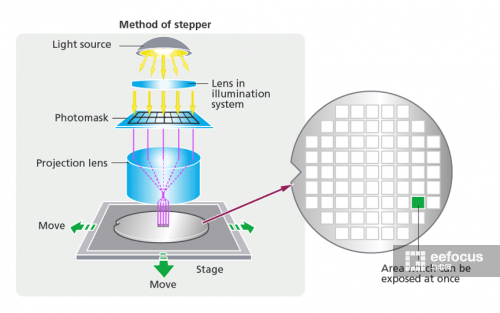

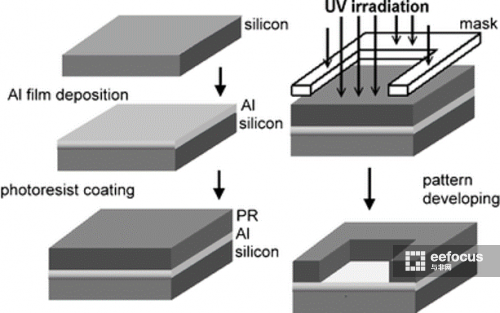

光刻

图源:Nikon

所谓的光刻工艺包括掩膜和光蚀刻两个部分。首先是将具有抗光蚀能力的光刻胶涂敷到晶圆上,在硅基表层形成电路图案,然后利用光对准器将晶圆对准掩膜,晶圆将透过掩膜镂空部分暴露在紫外线下,此时暴露部分的光刻胶变成可溶状态,从而将掩膜版上的电路结构临时复制到硅基上。

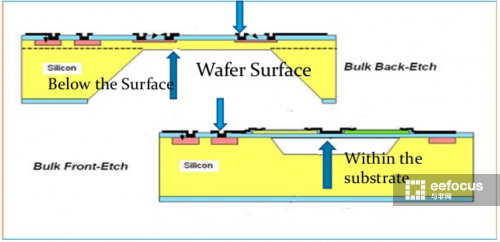

刻蚀

图源:SlideShare

按光刻机刻出的电路结构,在硅片上进行微观雕刻,刻出沟槽或接触孔。具体来说,刻蚀是利用显影后的光刻胶图形作为掩模,再借助化学液体或等离子体在衬底上腐蚀掉一定深度的薄膜物质,随后得到与光刻胶图形相同的集成电路图形。

离子注入

图源:格芯

离子注入是芯片制造工艺中的一种重要的掺杂技术,也是控制 MOSFET 阈值电压的一个重要手段。通常是在真空、低温的环境下,将磷化氢或三氯化硼杂质离子加速,获得有一定动能的杂质离子,然后将离子束摄到敷有光刻胶掩膜的晶圆上。有光刻胶掩盖的部分,离子束无法穿透光刻胶而被阻挡开来;没有掩盖的部分,离子束会被注入到衬底上,实现掺杂,而掺杂深度取决于离子束的能量。最后,在离子注入完成后,必须进行光刻胶的彻底清除工作,才能进入下一环节。

金属化

图源:Pinterest

金属化指的是采用沉积等方式将金属薄膜沉积到晶圆上,再通过金属薄膜光刻,形成表面金属连线,将各个元器件连接到一起的工艺。因此第一步就是要刻蚀出接触孔。第二步是制备金属薄膜,主要导电金属材料可能是铝合金或金,手段通常包括蒸发、溅射、金属 CVD 以及电镀等,目前金属 CVD 因具有很强的台阶覆盖能力、良好的高深宽比接触和无间隙式的填充特性而受到广泛应用。第三步是采用光刻和刻蚀工艺或剥离技术去除布线以外的部分,形成相互连接的金属导线。第四步是进行合金化的热处理,从而保证芯片和金属之间有较好的导电性。最后是平坦化,减少因晶圆表面的不平整度带来的光传播的精确度受损,从而影响其准确地进行图形制作的一种工艺。这种工艺不仅会被用到表层,当金属层增加的时候也会被用到中间层中。

晶圆测试

图源:知乎

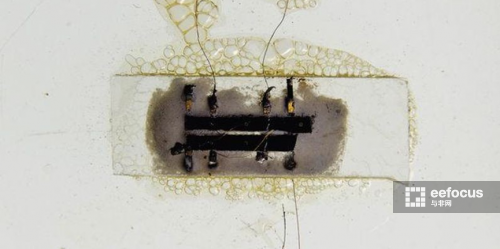

当载有集成电路的晶圆加工出来之后,需要对其进行测试,主要目的是减少封装的成本,提早筛选出有问题的集成电路模块(芯片原型)。具体操作是采用探针测试平台,在无尘室中根据事先定义好的测试点对芯片原型进行交直流、光照等电气性能测试。该测试通过治具可以对测试平台上的晶圆进行一次性测试,而无需对芯片逐一进行,因此测试效率较高。

切割与封装

图源:The CPU Shack

每个晶圆都包含数百至上万个芯片,通过金刚石锯将晶圆切割成单片,经过减薄工序,然后针对每一个单片(芯片)进行电气测试。如果测试结果有问题,这颗芯片就会被丢弃;如果测试结果合格,该芯片就会被送去封装。在封装前,将会使用显微镜对芯片进行复检,只有通过复检的芯片才会被真正封装起来。

封装测试

IC tester | 图源:Agilent

对于芯片来说,出厂前测试主要包含三个方面,前两项分别是晶圆测试和芯片测试,这两项在上一节中已经描述过了(见“切割与封装”章节)。而这里重点要将的其实是第三项测试:封装测试,也就是芯片出厂前测试。据统计,这三项测试将会占据整个芯片生产成本的比例高达 1/4 至 1/2。

此时的待测芯片已经包裹了一层封装,没有那么脆弱了,因此对于测试环境要求也没有那么严苛,不需要无尘室测试了。但是对于封装测试而言,由于封装本身的阻挡,测试探针无法触及芯片内部,测试范围受到限制的同时,也增加了测试的复杂度。

话不多说,一般的芯片封装测试包括各种环境下的消耗功率、发热量、运行速度、耐压度等多项电气特性测试,在测试过程中往往需要大量的编程、烧录验证工序。有的时候根据客户的要求,也会做一些针对性测试,看是否满足客户的需求。当测试结果一切正常,该芯片就会被打上规格、型号及出厂日期等丝印,等待打包出厂了。

国内外发展现状

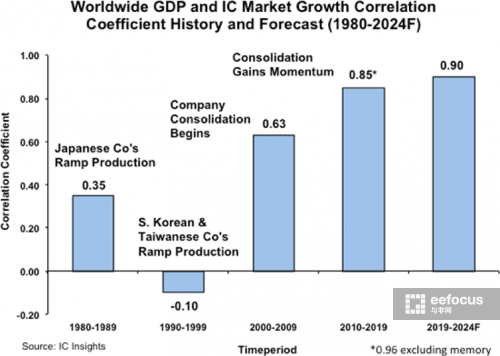

芯片市场行情

据 IC Insights 数据显示,IC 市场在不断扩大,成为越来越重要的 GDP 驱动力,预计 2019-2024 年的相关系数将达到 0.90,高于 2010-2019 年的 0.85。

图源:IC Insights

芯片设计

对于芯片设计而言可分为两大部分来讲,第一部分是 EDA(电子设计自动化)工具,第二部分是芯片设计。

首先来谈一谈EDA 工具,根据电子系统设计(ESD)联盟市场统计服务(MSS)发布了关于 EDA 行业 2019 年第二季度的调查报告显示,EDA 行业 2019 年第二季度收入为 24.721 亿美元,同比 2018 年第二季度的 23.185 亿美元,总体呈现增长态势,增长幅度为 6.6%。同时,将最近四个季度与前四个季度相比,四个季度的移动平均值增长了 6.0%。可见 EDA 工具需求度在不断上涨,市场前景广阔。然而从市场分布的角度看,却不太乐观。怎么说?目前全球 EDA 市场主要由 Cadence、Synopsys 和被西门子收购的 Mentor Graphics 三大巨头垄断,它们占全球市场的份额超过 60%。而中国的 EDA 工具产业却缺乏与先进工艺结合的机会,从而步步落后,缺少深亚微米的 EDA 成体系的设计平台。

图源:行芯科技

其次我们来谈一谈芯片设计,从市场分布的角度来讲,高通是当之无愧的手机芯片霸主,而计算机、服务器 CPU 则是由英特尔和 AMD 分食,对比之下,我国能拿得出手的应该就是华为的麒麟系列了。但明明我们大多数工程师都采用了和国外相同的 EDA 软件,除了 IP 限制以外,我想阻碍我国在芯片设计行业大展拳脚的最大因素肯定就是芯片设计高端人才了。但是人才不是一朝一夕能培养出来的,尤其是模拟芯片行业。相对来说,数字芯片由于经验依赖性小,是我国目前主攻的部分,尤其是 AI 时代的到来,以及中美贸易战的警钟督促,让本土芯片厂商寻到了一丝契机。

芯片制造、测试

从标题我们就可以看出本章节将会从芯片制造和封装测试两个角度来剖析。

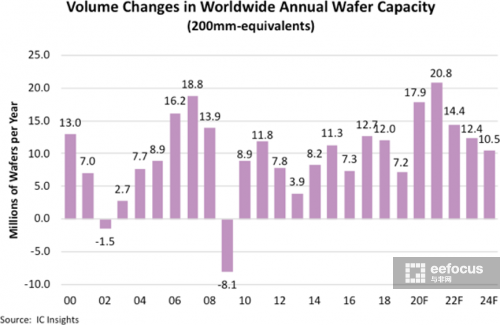

我们从芯片制造谈起,芯片行业应对芯片需求量上涨的方式不是增加单位晶圆的芯片数量,而是在不断增加晶圆的数据总量。据 IC Insights 预测,2020 年可能增加多达 1790 万个晶圆(200 mm 当量)的新 IC 产能,2021 年将再增加 2080 万个晶圆的产能。

图源:IC Insights

当然,如果有的人说,现在不是在不断扩大晶圆的尺寸吗?没错,但其主要目的是为了降低成本,而非应对数量需求上涨的主要手段。

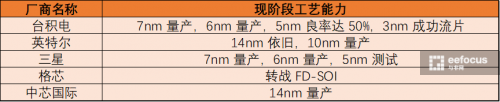

就目前晶圆代工(芯片制造)市场而言,目前全球主流的几家晶圆代工厂包括台积电、英特尔、三星、格芯和中芯国际。据统计,他们的工艺进阶如下图所示:

大家可以发现,对于芯片制造厂商而言,除了芯片 nm 级工艺以外,良率也是他们生产制造能力的主要考量因素。

我国在芯片制造行业虽显落后,但近些年的奋起直追,也诞生了像中芯国际、华虹半导体这样的本土巨头,成绩也算显著。只是在芯片制程设备方面还显沉重,尤其是光刻机这一块,已经成为制约我国芯片制造业的最大痛点。但在沉重中又有一丝欣慰,这欣慰来自于尹志尧等爱国人士的付出,他们的努力是我国的刻蚀设备走上了国际顶尖水平,目前已攻破 5nm 难关。

接下来,我们再来谈一谈封装测试,从全球范围来看,封装测试市场排名世界第一的是台湾地区的日月光公司,而出于成本和市场的考虑,不少半导体厂商选择将封测厂转移到中国,因此国内封测产业已经具备了一定的规模和技术基础。立足中国,差距在不断缩小,本土的长电科技、华天科技和通富微电发展也不错,对比芯片设计、制造行业而言,封测可以说是芯片产业中国内发展较好的一块了。

写在最后

对于芯片行业或者说集成电路行业来说,缺的从来不是市场,而是工艺、技术的比肩。对于像中国这样的发展中国家而言,我们从前落后,但当下我们可以抓住 AI 的机遇,让自己从低端市场向高端市场爬坡,挑战是不可避免的,沉下心来做技术才能成就一个产业。未来,无人可知,吾辈只需努力!

登录

登录

注册

注册